Hannover, Germania (CeBIT 2008) – AMD muove i suoi primi passi nell’era dei circuiti a 45 nanometri, una tecnologia che ha utilizzato per costruire due prototipi di processore quad-core, Shanghai e Deneb , rispettivamente pensati per i server (Opteron) e i PC desktop (Phenom).

Il chipmaker di Sunnyvale non ha ancora svelato le date di lancio delle due famiglie di CPU, ma il periodo approssimativo del debutto di Shanghai è stato confermato per la seconda metà dell’anno . Intel, come noto, ha introdotto i suoi primi chip a 45 nm lo scorso autunno, e all’inizio dell’anno ne ha commercializzati altri 16 modelli .

Il chipmaker di Sunnyvale non ha ancora svelato le date di lancio delle due famiglie di CPU, ma il periodo approssimativo del debutto di Shanghai è stato confermato per la seconda metà dell’anno . Intel, come noto, ha introdotto i suoi primi chip a 45 nm lo scorso autunno, e all’inizio dell’anno ne ha commercializzati altri 16 modelli .

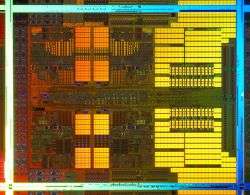

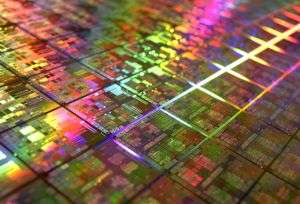

I due processori a 45 nm di AMD sono stati prodotti nell’impianto Fab 36 di Dresda, in Germania, su wafer da 300 millimetri. La fabbrica è stata da poco riconvertita al processo produttivo immersion lithography , che può essere impiegato per stampare pattern di circuiti con dimensioni inferiori a 45 nm. Tale tecnologia è stata sviluppata da AMD in collaborazione con IBM insieme ai transistor con gate metallici ad alta costante k (HK+MG), gli stessi utilizzati da Intel nei propri chip a 45 nm. A differenza di quanto riportato da alcune fonti, però, i primi processori a 45 nm di AMD non si avvarranno di quest’ultima innovazione: secondo quanto affermato da un portavoce del chipmaker, i transistor HK+MG saranno introdotti solo in un secondo momento .

AMD afferma che i benefici apportati dalla tecnologia HK+MG, relativi alla minore dispersione di corrente, sono in gran parte già garantiti dalla propria tecnologia strained silicon e da quella silicon-on-insulator di Big Blue. Ciò non toglie che i transistor con gate metallici rappresentino una tappa praticamente obbligata nello sviluppo di circuiti più piccoli, come quelli a 32 nm .

Di Shanghai, ossia l’Opteron di prossima generazione, sono già trapelati alcuni dettagli tecnici, il più importante dei quali è rappresentato dall’inclusione di una cache L3 da 6 MB : si tratta di un grande passo in avanti rispetto ai 2 MB attualmente inclusi in Barcelona , soprattutto considerando che questa cache è condivisa da quattro core.

Di Shanghai, ossia l’Opteron di prossima generazione, sono già trapelati alcuni dettagli tecnici, il più importante dei quali è rappresentato dall’inclusione di una cache L3 da 6 MB : si tratta di un grande passo in avanti rispetto ai 2 MB attualmente inclusi in Barcelona , soprattutto considerando che questa cache è condivisa da quattro core.

AMD ha anche promesso di ridurre la latenza della cache L3 , una miglioria che nel 2009 dovrebbe affiancarsi alla tecnologia G3MX , che permetterà di incrementare significativamente la quantità di memoria gestibile dal processore e, nell’ugual tempo, aumentare la velocità dell’interfaccia con la memoria. Una soluzione a cui Intel dovrebbe rispondere con la propria tecnologia QuickPath , una connessione point-to-point che aggirerà finalmente i limiti dell’attuale front-side bus.