Taipei – Ha i colori di tre diversi paesi l’inedita alleanza appena stipulata tra Intel , Samsung e la più grande fonderia di semiconduttori al mondo, la taiwanese TSMC , per incrementare la dimensione dei wafer di silicio e, di conseguenza, l’efficienza dei processi di produzione dei chip.

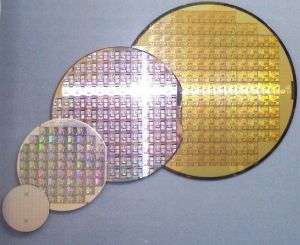

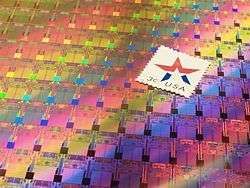

I wafer (v. immagine a destra) sono costituti da una sottile piastra circolare di materiale semiconduttore su cui vengono costruiti i chip: generalmente, maggiore è il diametro di tale piastra e migliore è la resa produttiva . Oggi lo stato dell’arte è rappresentato da wafer con 300 millimetri di diametro, tipicamente in grado di contenere centinaia o migliaia di circuiti integrati. Intel e soci intendono sviluppare le tecnologie e le apparecchiature necessarie alla fabbricazione di wafer da 450 mm , che potranno ospitare un numero di die stampati (ad esempio, quelli dei processori per computer) più che raddoppiato rispetto agli attuali wafer da 300 mm.

I wafer (v. immagine a destra) sono costituti da una sottile piastra circolare di materiale semiconduttore su cui vengono costruiti i chip: generalmente, maggiore è il diametro di tale piastra e migliore è la resa produttiva . Oggi lo stato dell’arte è rappresentato da wafer con 300 millimetri di diametro, tipicamente in grado di contenere centinaia o migliaia di circuiti integrati. Intel e soci intendono sviluppare le tecnologie e le apparecchiature necessarie alla fabbricazione di wafer da 450 mm , che potranno ospitare un numero di die stampati (ad esempio, quelli dei processori per computer) più che raddoppiato rispetto agli attuali wafer da 300 mm.

Grazie all’incremento delle rese produttive, e alla riduzione delle risorse – acqua, energia ecc. – necessarie per la produzione di ogni singolo circuito stampato, la produzione di chip con wafer di dimensioni maggiori consente alle aziende di fabbricare semiconduttori a costi inferiori . I vantaggi non sono soltanto economici, ma anche ambientali: ad esempio, Intel afferma che con la migrazione dai wafer da 200 mm a quelli da 300 mm sia stato possibile ridurre significativamente tanto le emissioni di inquinamento atmosferico e di gas serra quanto il fabbisogno idrico.

Secondo Intel, Samsung e TSMC, nello sviluppo dei nuovi wafer da 450 mm il settore dei semiconduttori può massimizzare il ritorno sugli investimenti e ridurre sostanziale costi di ricerca e sviluppo, applicando standard comuni, razionalizzando le modifiche rispetto all’infrastruttura e impegnandosi verso un obiettivo temporale comune. Le aziende concordano inoltre che, tramite un approccio cooperativo, sarà possibile ridurre i rischi e i costi della transizione.

“La transizione ai wafer da 450 mm offrirà vantaggi all’intero ecosistema del settore dei circuiti integrati, e Intel, Samsung e TSMC collaboreranno con fornitori e altri produttori di semiconduttori per sviluppare attivamente le risorse necessarie per questo tipo di wafer”, ha affermato Cheong-Woo Byun, senior vice president del Memory Manufacturing Operation Center di Samsung. “L’aumento dei costi dovuto alla complessità delle tecnologie più evolute è una delle maggiori preoccupazioni del futuro”, ha poi aggiunto Mark Liu, senior vice president dell’Advanced Technology Business di TSMC. “Intel, Samsung e TSMC ritengono che la transizione ai wafer da 450 mm costituisca una soluzione potenziale per mantenere una struttura a costi ragionevoli per il settore”.

“La transizione ai wafer da 450 mm offrirà vantaggi all’intero ecosistema del settore dei circuiti integrati, e Intel, Samsung e TSMC collaboreranno con fornitori e altri produttori di semiconduttori per sviluppare attivamente le risorse necessarie per questo tipo di wafer”, ha affermato Cheong-Woo Byun, senior vice president del Memory Manufacturing Operation Center di Samsung. “L’aumento dei costi dovuto alla complessità delle tecnologie più evolute è una delle maggiori preoccupazioni del futuro”, ha poi aggiunto Mark Liu, senior vice president dell’Advanced Technology Business di TSMC. “Intel, Samsung e TSMC ritengono che la transizione ai wafer da 450 mm costituisca una soluzione potenziale per mantenere una struttura a costi ragionevoli per il settore”.

Le tre partner prevedono di avviare la prima linea produttiva con wafer da 300 mm nel corso del 2012 , ma la transizione verso questo nuovo formato potrebbe richiedere diversi anni.